Tài liệu Thư viện số

- Giáo trình SPKT (418 )

- Luận văn, luận án (2865 )

- Đồ án, khóa luận tốt nghiệp (9613 )

- Tài liệu tham khảo (1350 )

- BC nghiên cứu khoa học (1589 )

- Kỷ yếu hội thảo (12 )

- Tạp chí khoa học (62 )

- Luật (349 )

- Cơ khí chế tạo máy (2344 )

- Điện - Điện tử (4378 )

- Cơ khí động lực (1242 )

- Xây dựng - Kiến trúc (3233 )

- Thực phẩm, Môi trường (1087 )

- Công nghệ thông tin (3074 )

- Kinh tế - Quản lý (4140 )

- In - Truyền thông (383 )

- CN May - thời trang (832 )

- Nghệ thuật - Ẩm thực (1516 )

- Nông - Lâm - Ngư Nghiệp (763 )

- Y học - Sức khỏe (620 )

- Khoa học xã hội (3535 )

- Lịch sử - Địa lý - Du lịch (492 )

- Khoa học tự nhiên (2112 )

- Văn học (2585 )

- Ngôn ngữ (4289 )

- Khoa học ứng dụng (408 )

- Thông tin Tuyển sinh (61 )

- Thông tin -Thư viện (418 )

- Thể loại khác (1376 )

Danh mục TaiLieu.VN

- Mẫu Slide Powerpoint

- Kinh Doanh Marketing (39320)

- Kinh Tế - Quản Lý (30571)

- Biểu Mẫu - Văn Bản (123435)

- Tài Chính - Ngân Hàng (23744)

- Công Nghệ Thông Tin (56521)

- Tiếng Anh - Ngoại Ngữ (9738)

- Kỹ Thuật - Công Nghệ (44193)

- Khoa Học Tự Nhiên (27343)

- Khoa Học Xã Hội (43227)

- Luật - Kinh tế luật (6560)

- Văn Hoá - Thể thao - Du Lịch (71283)

- Y - Dược - Sức Khoẻ (83234)

- Nông - Lâm - Thuỷ sản (16418)

- Luận Văn - Báo Cáo (217024)

- Tài Liệu Phổ Thông (244133)

- Trắc Nghiệm Online (213578)

- Trắc Nghiệm MBTI

- Trắc Nghiệm Holland

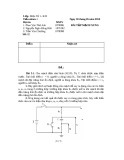

THIẾT KẾ, MÔ PHỎNG BỘ LỌC NHIỄU TÍN HIỆU ĐIỆN TIM DÙNG MATLAB VÀ CHUYỂN MÃ VHDL

Xây dựng một bộ lọc số trên nền tảng FPGA để lọc nhiễu tín hiệu điện tim ECG nhằm đem lại tín hiệu xác thực nhằm hỗ trợ tốt hơn cho việc khám chữa bệnh. Trong đó, FPGA được xem như là phần cứng với chức năng thực thi bộ lọc nhiễu cho tín hiệu điện tim, còn Matlab được sử dụng như một công cụ để thiết kế và mô phỏng bộ lọc nhằm đánh giá khả năng thực hiện trong thực tế.

Từ khóa: THIẾT KẾ, MÔ PHỎNG BỘ LỌC NHIỄU TÍN HIỆU ĐIỆN TIM DÙNG MATLAB VÀ CHUYỂN MÃ VHDL , TRẦN THANH LÂM

22 p ovanke 06/09/2019 884 6

Bạn đang xem trang mẫu tài liệu này.